# 基于 FPGA 的 DDS 调频信号的研究与实现

#### 石伟 宋跃 李琳

(湖南科技大学 湖南湘潭 411201)

摘 要:本文从 DDS 基本原理出发,利用 FPGA 来实现 DDS 调频信号的产生,重点介绍了其原理和电路设计,并给出了 FPGA 设计的仿真和实验,实验结果表明该设计是行之有效的。

关键词: DDS;调频;FPGA;仿真

中图分类号: TP274; TM935 文献标识码: A

## Realization of DDS Frequency Modulate Signal on FPGA

SHI Wei, SONG Yue & LI Lin,

(College of Physical, Hunan University of Science and Technology Hunan Xiangtan 411201)

**Abstract:** According to the principium of Direct Digital Synthesis, DDS frequency modulated signal was generated by FPGA, the principium and circuit design were mainly introduced, the imitation and experiment of FPGA design were given, the experiment result showed the design was feasible.

Keywords: DDS; Frequency modulation; FPGA; Imitation

### 1 引言

直接数字频率合成器 (DDS) 技术,具有频率切换速度快,很容易提高频率分辨率、对硬件要求低、可编程全数字化便于单片集成、有利于降低成本、提高可靠性并便于生产等优点。目前各大芯片制造厂商都相继推出采用先进 CMOS 工艺生产的高性能和多功能的 DDS 芯片,专用 DDS 芯片采用了特定工艺,内部数字信号抖动很小,输出信号的质量高。然而在某些场合,由于专用的 DDS 芯片的控制方式是固定的,故在工作方式、频率控制等方面与系统的要求差距很大,这时如果用高性能的 FPGA 器件设计符合自己需要的 DDS 电路就是一个很好的解决方法,它的可重配置性结构能方便的实现各种复杂的调制功能,具有很好的实用性和灵活性。

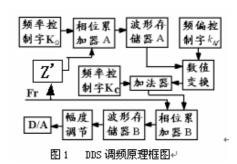

## 2 DDS 调频信号发生器框图设计

设调制信号为 $u_{O}(t) = U_{OM} \cos \Omega t = U_{OM} \cos(2\pi f_{O}t)$

载波为 $u_c(t)=U_{cM}\cos\omega_c t=U_{cM}\cos(2\pi\!f_c t)$  ,设相位累加器位数为x  $(P_0=2^x)$  ,系统时标为

$f_r$ ,调制信号为 $f_\Omega$ ,分频系数为Z',则调制信号时钟 $f_{rh}=rac{f_r}{Z'}$ ,则相位累加器 B 累加次数i 与

相位累加器 A 累加次数 j 之间存在关系  $j = floor(\frac{i}{Z'})$  ,故可得出

调制信号为

$$u_{\Omega}(jT_r) = U_{\Omega M} \cos(\frac{2\pi k_{\Omega}}{P_0} floor(\frac{i}{Z'}))$$

载波为

$$u_c(iT_r) = U_{cM} \cos(2\pi i k_c/P_0)$$

其中调制波频率控制字  $k_{\Omega}=\frac{f_{\Omega}P_{0}}{f_{rb}}$  ,载波频率控制字  $k_{c}=\frac{f_{c}P_{0}}{f_{r}}$  。

1

由此可得调频波频率控制字  $k=k_c+k_{\Delta f}\cos(\frac{2\pi k_{\Omega}}{P_0}floon(\frac{i}{Z'}))$  ( $k_{\Delta f}$  为频偏控制字)

故 DDS 调频公式为

$$u_{pm}(iT_r) = U_{cM}\cos(\frac{2\pi}{P_0}\sum_0^i(k_c + k_{\Delta\!f}\cos(\frac{2\pi k_\Omega}{P_0}floor(\frac{i}{Z'}))))$$

### 3 DDS 调制信号发生器 FPGA 电路设计

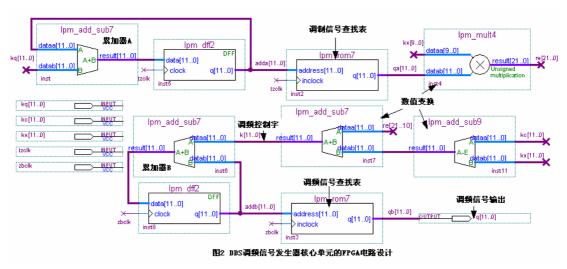

图 2 给出了 DDS 调制信号发生器核心单元的 FPGA 电路设计图。其设计方案采用 ALTERA 公司的 Cyclone 系列 EP1C6T144C6 芯片,加法器为 12 位,调制信号波形存储器为 4096 x 12BIT,载波信号波形存储器为 4096 x 12BIT,系统时钟为 80MHz;设计性能参数:载波频率可达 10MHz (为确保波形不失真,一周期至少取 8 点),调制频率范围 0~100K,调频深度 0~10。外部电路输入有调制信号频率控制字 Kh[11..0],载波信号频率控制字 Kc[11..0],频偏控制字 Kx[11..0],调制信号系统时钟TZCLK,载波信号系统时钟ZBCLK。Kh[11..0]经累加器 A 输出累加相位 ADDA[11..0]作为调制信号查找表的地址,波形数据 Qa[11..0]和 Kx[11..0]和 Kc[11..0]经过数值变换后输出调频控制字 K[11..0]。K[11..0]经累加器 B 输出累加相位 ADDB[11..0]作为调频信号查找表的地址,波形数据 Qb[11..0]经外部 DAC 转换和低通滤波得到调频信号波形。其中,在两个累加器后相连的DFF 缓冲器有助于消除毛刺的影响,进一步确保系统的稳定性和可靠性。

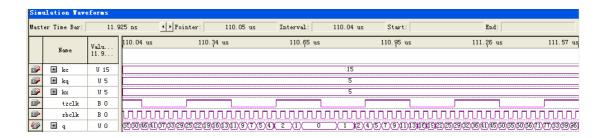

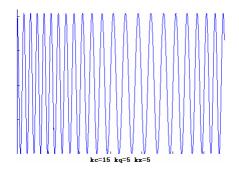

# 4 仿真及实验

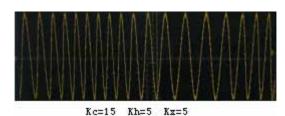

取载波系统时标频率 1MHz,调制信号系统时标频率 100KHz,相位累加器位数 8 位,两个波形存储器地址位数和数据位数都为 8 位。用 QUERTUS 3.0 仿真,见图 3;用 matlab 6.5 仿真见图 4;用 AEDK-EDA 实验箱下载(其 FPAG 芯片为 EPF10K10TC144-4),D/A 转换及单极性输出电路用 ispPAC20 芯片实现,通过 Tektronix TDS3054B 示波器观察波形,结果见图 5 。其中 D/A 位数为 8,测量范围-4—4V,载波信号峰值 1 . 414V,由图 4 和图 5 频率调制解调波形数据可得载波频率为 14.2kHz,误差-3.06%;调制频偏为 480Hz,误差-1.69%;调制度为 M=10.21%,误差 2.1%,调制频率为 4.82kHz,误差-1.23%。从实验结果可以看出本文提供的设计理论及设计电路的不但正确、可行,并具有良好的性能参数。所有设计、仿真及实验结果的一致,为 DDS 调频信号发生器 FPGA 实现提供了优良的设计方案。

图 3 DDS 调频波仿真图 (QUERTUS II)

图 4 DDS 调频波仿真图 (matlab)

图 5 DDS 调频波实验结果图

#### 5 总结

用 FPGA 实现 DDS 调频信号电路较采用专用 DDS 芯片更为灵活,只要改变 FPGA 中 ROM 内的数据和控制参数,DDS 就可以产生任意调制波形,且分辨率高,具有相当大的灵活性。相比之下,DDS 的功能完全取决于设计需求,可以复杂也可以简单,而且 FPGA 芯片还支持在系统现场升级。另外,将 DDS 设计嵌入到 FPGA 芯片所构成的系统中,其系统成本并不会增加多少,而购买专用芯片的价格则是前者的很多倍。所以采用 FPGA 来设计 DDS 系统具有很高的性价比。

#### 参考文献

- [1] 戴 柠.陈一饶. DDS 信号源的研制[J]. 仪器仪表学报.1996,17(1):24-28.

- [2] Jenq Y C.Digtal spectra of nonuniformly sampled signals:fun damentals and high speed wave form digitizers[J].IEEE Trans IM,1998, 37(2):245-251.

- [3] 王秋生.王 祁.孙圣和.直接数字合成调频信号的研究[J].仪器仪表学报.2000,4(21):428-430

- [4] Timo Rahkonen. Harri Eksyma..Antti Mantyniemi. Heikki Repo. A DDS Synthesizer with Digital Time Domain Interpolator. Analog Integrated Circuits and Signal Processing. 2001,27:109–116.

- [5] Amir M. Sodagar, G. Roientan Lahiji, Ali Azarpeyvand .Reduced-Memory Direct Digital Frequency Synthesizer Using Parabolic Initial Guess. Analog Integrated Circuits and Signal Processing, 2003,34: 89–96.

- [6] Abdellatif Bellaouar, Michael S. O'brecht. Low-Power Direct Digital Frequency Synthesis forWireless Communications. IEEE Journal of Solid-State Circuits/the Institute of Electrical and Electronics Engineers.2000.35(3):385-390.

- [7] 褚振勇.翁木云. FPGA 设计及应用[M]. 西安: 西安电子科技大学出版社, 2002.

#### 作者简介

石 伟: 男,汉族,1975 年生,湖南株洲人,硕士研究生,湖南科技大学物理学院讲师。研究方向为数据采集、微机开发与应用等。

宋 跃:男,汉族,1963 年生,湖南邵阳人,教授,硕士生导师,湖南科技大学电子信息工程系主任。研究方向为数据采集、微机开发与应用、高校教学与实验改革等,主持本系列项目研究。